Arm DesignStart Cortex-M1の環境にはRTLシミュレーション環境があるので、それを試してみる。

もちろん、Cortex-M1自体は暗号化されていて中身は見えないので、SoC環境を構築してRTLシミュレーションし、その波形を観測することになる。

QSPIメモリモデルのダウンロード

Arty-A7のボードにはQSPIメモリとしてN25Q128A13Eが搭載されている。

QSPI付きのシミュレーションを行うために、Micronのウェブサイトからモデルをダウンロードしてテストベンチ環境に配置する。

hardware/m1_for_arty_a7/testbenchにMicron_N25Q128A13Eディレクトリを置き、さらにMicron_N25Q128A13E/sim/sfdp.vmfをtestbenchディレクトリにシンボリックリンクした。

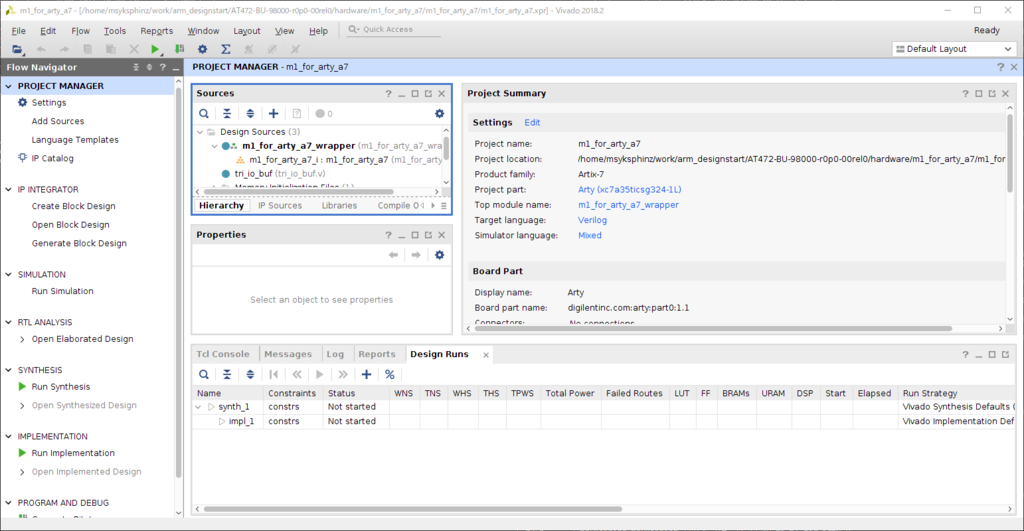

そしてAT472-BU-98000-r0p0-00rel0/hardware/m1_for_arty_a7/m1_for_arty_a7m1_for_arty_a7.xprをVivadoで開いた。

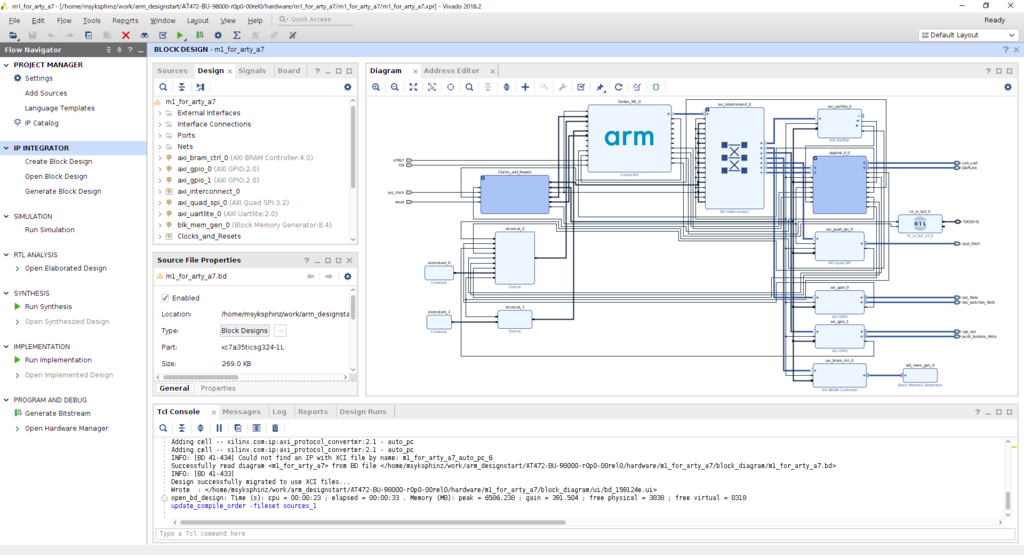

m1_for_arty_a7_iインスタンスをダブルクリックすると、以下のブロック図が表示された。

次に、シミュレーションを行うのだが、QSPIのモデルをダウンロードしているのでdefineを変更する。

AT472-BU-98000-r0p0-00rel0/hardware/m1_for_arty_a7/testbench/tb_m1_for_arty.v

// Uncomment this if the model for the Micron and Spansion QSPI devices has been downloaded // and installed in the appropriate directory. If this is not defined, the testbench will issue // an error message if there are any attempts to read or write to the QSPI `define INCLUDE_QSPI_MODEL 1

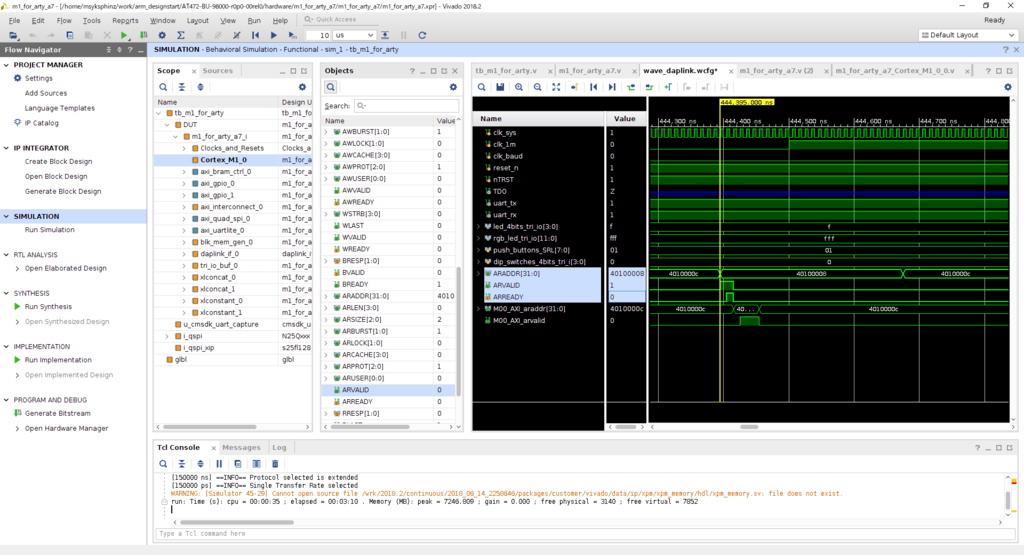

Flow Navigatorから[SIMULATION]のプロパティを開き、デフォルトのシミュレータをQuestaSimからVivado Simulatorに変更する。 そして、Run Simulationでシミュレーションを実行した。波形が表示されたが、とりあえず動いているような感じがしている。

ただしよく見てみるとなんだかおかしい。Cortex-M1が最初に出してくるフェッチが0x40100008という不思議な場所から開始している。これはArmの特徴なのか?このボードの特徴なのか、不具合なのか、良く分からない。