2018/11/01追記。だいぶ増えてきた。表更新。

2019/04/17追記。S21を追加。

| |

U74-MC |

U74 Standard |

S76-MC |

S76 Standard |

E76-MC(Main-Core) |

E76-MC(Sub-core) |

E76 Standard |

| Core Type |

U74 RV64C |

S7 RV64IMAC |

RV64GC |

RV64GC |

RV64GC |

RV32IMAFC |

RV32IMAFC |

| L1 Icache |

32kB |

16kB |

32kB |

32kB, ITIM option |

32kB, ITIM option |

32kB, ITIM option |

32kB, ITIM option |

| L1 Dcache |

32kB |

8kB DTIM |

32kB |

32kB, FIO RAM option |

32kB, FIO RAM option |

32kB, FIO RAM |

32kB, FIO RAM |

| Memory Protection |

8 |

8 |

8 |

|

|

|

|

| Local Interruption Per Core |

|

|

|

|

|

|

|

| Core Local Interrupt |

CLIC |

- |

CLIC |

|

|

|

|

| Virtual Memory Support |

Sv39 |

- |

Sv39 |

|

|

|

|

| L2 ECC |

2MB |

|

128kB |

|

|

|

|

| DMIPS/MHz |

2.5 |

|

2.5 |

|

2.5 |

2.3 |

2.3 |

| Coremark/MHz |

4.9 |

|

4.9 |

|

4.9 |

4.9 |

4.9 |

| Pipeline |

|

|

|

In-order, 8-stage |

In-order, 8-stage |

8-stage |

8-stage |

| |

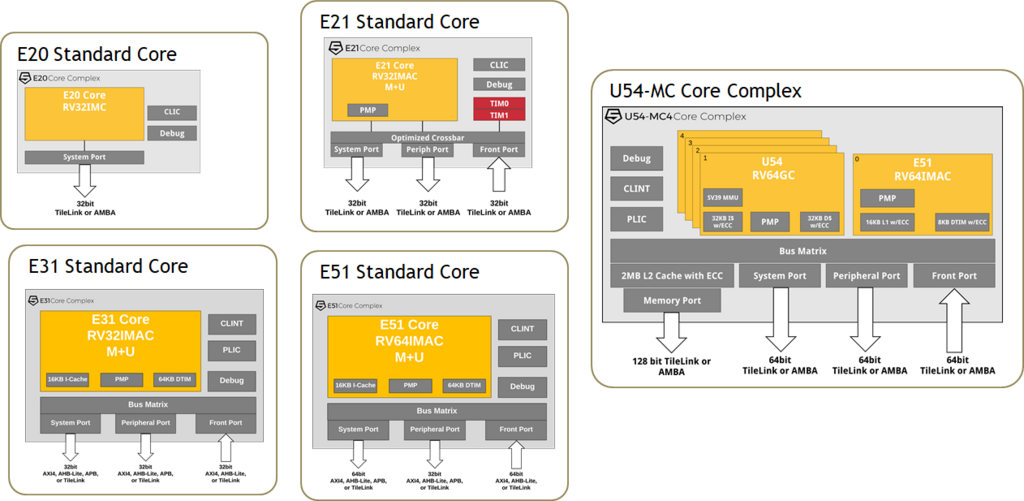

U54‑MC(Main-Core) |

U54‑MC(Sub-Core) |

S54 Standard Core |

S51 Standard Core |

| Core Type |

U54 RV64GC |

E51 RV64IMAC |

RV64IMAFDC |

RV64IMAC |

| L1 Icache |

32kB |

16kB |

16kB, ITIM option |

16kB, ITIM option |

| L1 Dcache |

32kB |

8kB DTIM |

64kB DTIM |

64kB DTIM |

| Memory Protection |

8 |

8 |

8 |

8 |

| Local Interruption Per Core |

48 |

48 |

16 |

16 |

| Core Local Interrupt |

- |

- |

1 timer, 1SW |

1 timer, 1 SW |

| Virtual Memory Support |

Sv39 |

- |

Up to 40 physical address |

- |

| L2 ECC |

2MB |

|

- |

- |

| DMIPS/MHz |

1.7 |

1.61 |

1.7 |

1.7 |

| Coremark/MHz |

2.75 |

2.73 |

3.01 |

3.01 |

| Pipeline |

|

|

In-order, 5-6stage |

In-order, 5-6stage |

| |

E34 Standard Core |

E31 Standard Core |

E24 Standard Core |

E21 Standard Core |

E20 Standard Core |

S21 |

| Core Type |

RV32IMAFC |

RV32IMAC |

RV32IMAFC |

RV32IMAC |

RV32IMC |

RV64IMAC |

| L1 Icache |

16kB, ITIM option |

16kB, ITIM option |

- |

- |

- |

- |

| L1 Dcache |

64kB, DTIM support |

64kB, DTIM support |

- |

- |

- |

- |

| Memory Protection |

8 |

8 |

8 |

2 |

- |

Up to 8 |

| Local Interruption Per Core |

16 |

16 |

? |

127 |

- |

Up to 1024 |

| Core Local Interrupt |

1 timer, 1 SW |

1 timer, 1 SW |

1024 Interrupts |

127 Interrupts |

32 Interrupts |

CLIC with 127 interrupts |

| Virtual Memory Support |

- |

- |

- |

- |

- |

- |

| L2 ECC |

- |

- |

- |

- |

- |

- |

| DMIPS/MHz |

1.61 |

1.61 |

1.38 |

1.38 |

1.1 |

1.6 |

| Coremark/MHz |

3.01 |

3.01 |

3.1 |

3.1 |

2.4 |

3.2 |

| Pipeline |

In-order, 5-6stage |

In-order, 5-6stage |

3-stage |

3-stage |

2-stage |

- |