これまでの記事はこちら。

- RISC-Vの連載をInterface誌に寄稿しました(2018年2月号から)

- RISC-Vの連載第2回がインターフェース誌に掲載されました

- RISC-Vの連載第3回がインターフェース誌に掲載されました

- RISC-Vの連載第4回がインターフェース誌に掲載されました

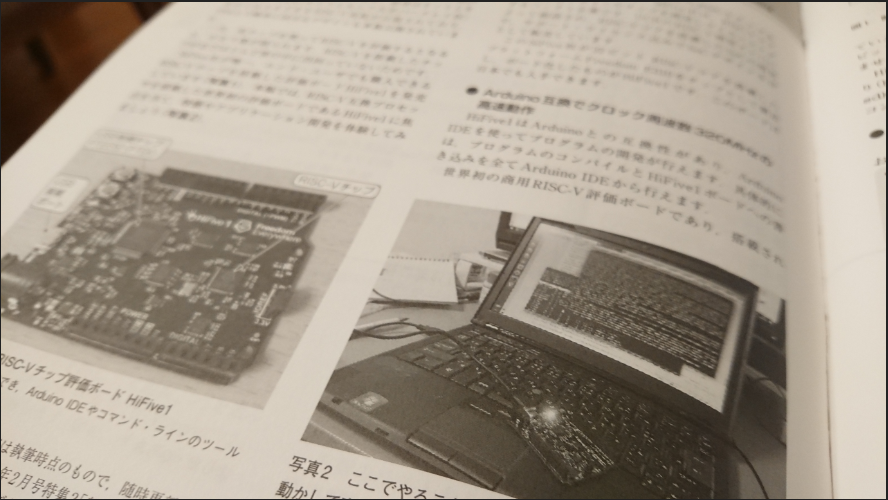

図. 第5回ではRISC-VボードHiFive1を使います。

今回は実機を触るということでRISC-VのASICチップHiFive1を使います。

HiFive1を動かすためにはいろんな方法があって、連載の中でも解説してますが、Arduinoの環境を使っていたり、Freedom SDKキットを使ったりと様々な方法があります。

今回は、とりあえず基本的な環境のセットアップの方法と、あとはベンチマークプログラムとしてCoreMarkを動かします。 CoreMarkが動いてしまえばそのボードはもう動いたようなもの!という勝手な感触で進めております...

あとはサイクルカウンタの使い方。これはRISC-Vに特有の問題ではありませんが、サイクルカウンタが64ビットで32ビットずつ別々のレジスタに分かれている場合、ちょっと変わったサイクルの取り出し方をしますよね。

- 上位32ビット(1)を取り出す。

- 下位32ビットを取り出す。

- 上位32ビット(2)をもう一度取り出す。

- (1)と(2)が異なっていればもう一度やり直し

これは2つのレジスタでサイクルカウンタが桁上げをしてしまい値がおかしくなることを防ぐためで(まあ桁上げの瞬間をキャプチャすることってなかなか無いだろうけど)、こういうテクニックはマイコンではよく使いますよね。

次回はHiFive1をつかってもうちょっと複雑なプログラムを動かす...と思われます。