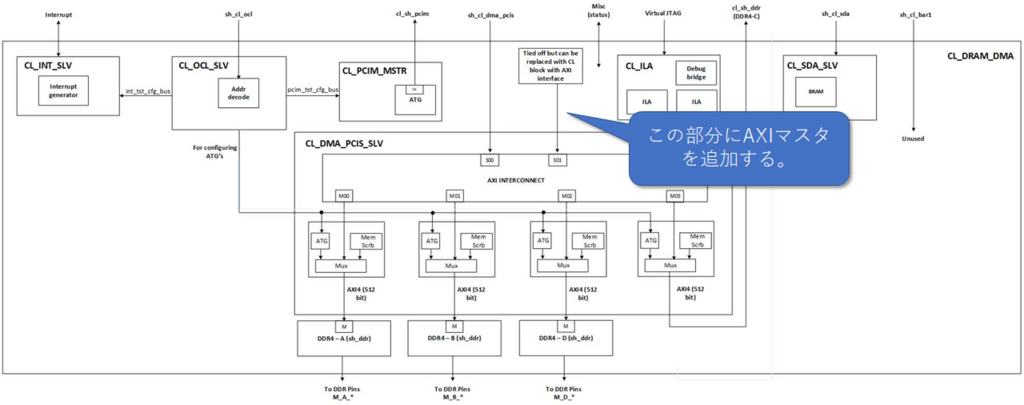

AWS F1インスタンス HDK の勉強を続けている。 目標としては、以下の部分にAXIマスタを接続してDRAMにアクセスし、データをフェッチする。

- DMAでホストからデータをDDR4メモリに格納する。

- AXIマスタデータをフェッチする

- 演算し、結果を格納する。

として、例えば行列積のアクセラレータをF1インスタンス上で動作させてみたい。

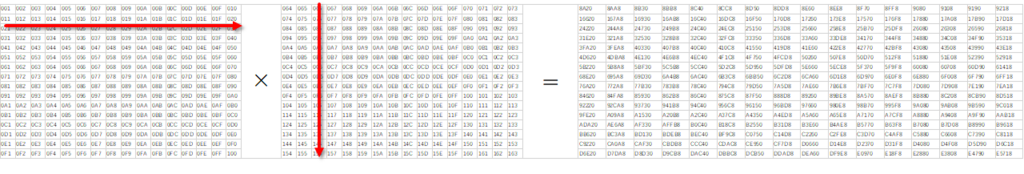

というわけで、とりあえず簡易的な行列演算回路、というか Dot Product Accelerator を作ってみた。 これでシミュレーションを実行してみる。 まずは簡単に、16x16の行列積を計算するための、16要素同士の32bit整数のDot Productを計算する。これをホストから16×16回アドレスを変えながら実行し、行列積を実行する。

とりあえず256要素分を全部計算すると時間がかかるので、以下の青色の部分だけを計算するようにプログラムを切り替えてシミュレーションを実行した。

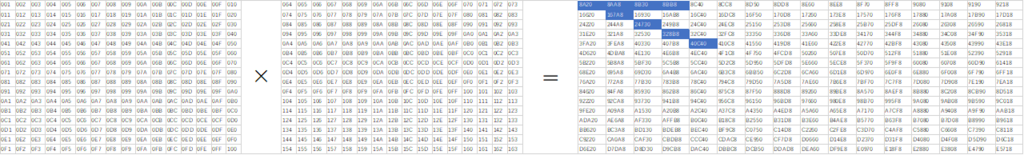

計算結果のログを抽出すると、以下のようになる。正しく計算できていることが確認できた。

今度は計算性能を上げる改造と、F1インスタンスを使ったFPGAでの動作を確認していく。

35594000 : [matrix] result FIFO read 0000000000008a20

38094000 : [matrix] result FIFO read 0000000000008aa8

40878000 : [matrix] result FIFO read 0000000000008b30

43270000 : [matrix] result FIFO read 0000000000008bb8

45778000 : [matrix] result FIFO read 00000000000167a8

48642000 : [matrix] result FIFO read 0000000000024730

50750000 : [matrix] result FIFO read 00000000000328b8

53262000 : [matrix] result FIFO read 0000000000040c40