RISC-V はどのようなターゲットにも適用することの出来るCPUアーキテクチャを目指している。 それはMPU(Micro Processor Unit) だけでなく MCU(Micro Controller Unit)としても活用することができる。

MCUで多く使用される(MPUもだろうけど) メモリ保護の機構についても、RISC-Vで定義されている。 大きく分けて、 PMA(Physical Memory Attribute) と PMP(Physical Memory Protection) である。 PMAはハードウェアで設定されているメモリマップ属性、PMAはソフトウェアで設定することのできるメモリマップ属性だ。

まずは、PMP(Physical Memory Protection) について仕様を見てみよう。 RISC-V Privileged Mode Manual Ver.1.10 を参照しながら、読み解いていこう。

物理メモリのプロテクション (Physical Memory Protection: PMP)

PMA(Physical Memory Attribute)が、ハードウェア的にメモリアクセスの属性を定義する機構であることに対し、PMP(Physical Memory Proctection)はソフトウェアによるメモリ領域の保護機構である。 PMPによるチェックはPMAと同時にチェックされる。

PMPアクセスもPMAと同様に、すべてのメモリアクセス(Read/Write/命令フェッチ)に適用される。 ただし、いくつか制約があり、

- S-Mode/U-Modeの場合はすべてのメモリアクセス(Read/Write/命令フェッチ)に対してPMPが適用される。

- mstatusレジスタのMPRVビットが設定されており、mstatusレジスタのMPPフィールドにS-Mode/U-Modeが設定されている場合に、ロード・ストア操作に対してPMPが適用される。

PMPチェックはすべてのページテーブルアクセスに対してもチェックされる。

また別のケースとして、PMPレジスタ自体がロックされている場合にはM-Modeでも適用されるケースがある。

PMPのCSRレジスタ構成

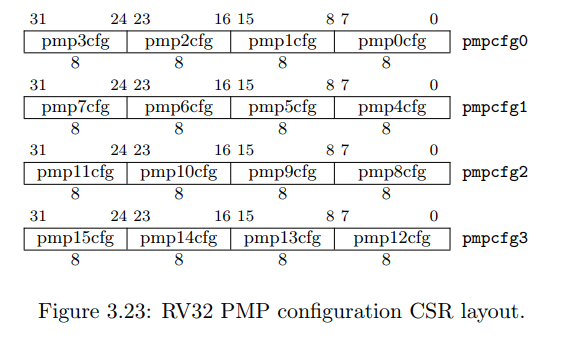

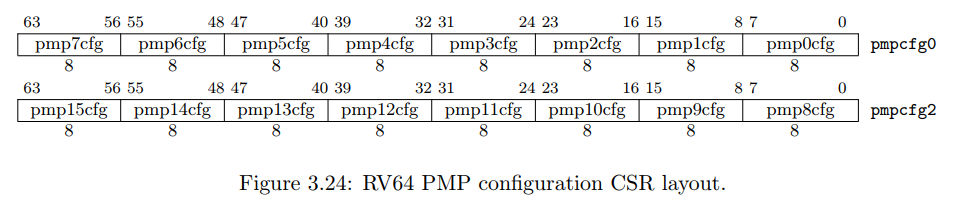

まずはpmpcfgから見ていこう。RV32とRV64では構成が異なるので要注意である。

PMPは現在の構成では16種類設定できるようになっている。

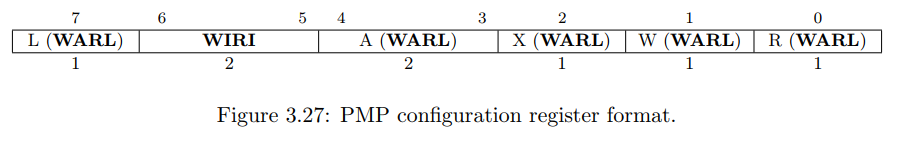

このpmpcfgレジスタのレジスタレイアウトだが、以下のようになっている。

- Lビット : Lockビット。pmpcfgレジスタのRWを設定する。

- Aビット : アドレスマッチングのためのモード

- X/W/R ビット : メモリアクセスのためのフィールド

これらについては詳細を後に見ていく。

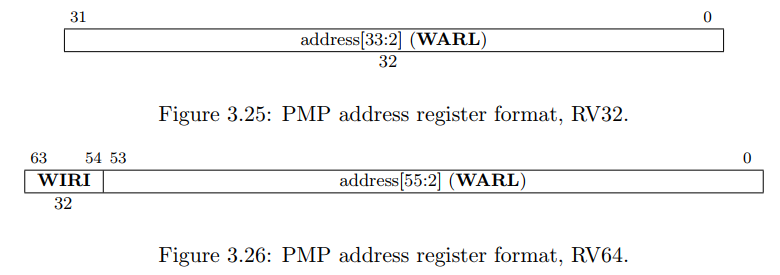

次にpmpaddrだ。これはpmpcfgと対になって使用される。こちらもRV32とRV64で構成が異なっている。

アドレスマッチングの方法

- アドレスをどのようにして判定するか

- アクセス許可の判定方法

の2つに大別される。まずはアドレスマッチングの方法について見ていく。

アドレスマッチング方式の種類

アドレスマッチング方式についてはpmpcfg のAビットで設定される。Aビットは2ビット長であり以下のエンコーディングで設定される。

| A | 名前 | 説明 |

|---|---|---|

| 0 | OFF | Null領域(PMP無効) |

| 1 | TOR | Top領域 |

| 2 | NA4 | 4バイト領域にアラインするモード |

| 3 | NAPOT | 8バイト以上で2の累乗の領域でアラインするモード |

TORの意味は、そのレジスタで設定されたアドレスは、アドレスマッチングの上位のアドレスであることを示している。例えばpmpcfg[i]レジスタでTORを設定すると、pmpaddr[i]とpmpaddr[i-1] で指定される領域でアドレスマッチングが行われる。もしi=0の領域でTORを設定した場合、0<addr<pmpaddr[0] までがアドレス設定領域として指定される。

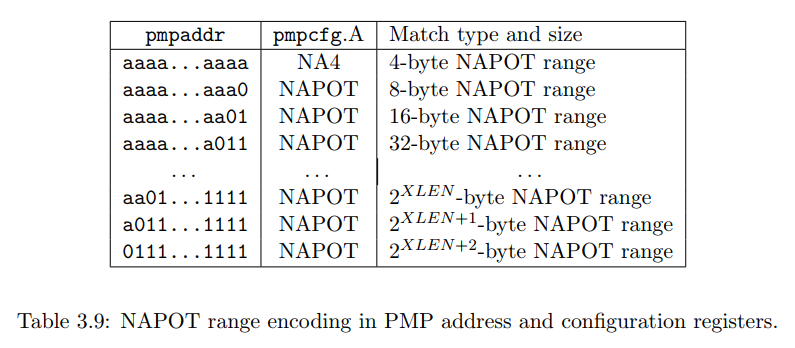

一方でNAPOT / NA4はアドレスマスクを使ってアドレス領域を設定する。以下のようなイメージだ。つまり、NA4はNAPOTの1種類ととらえることができるだろう。

PMPレジスタのアドレスマッチングは、下位のレジスタ番号から順に適用される。M-Modeの場合、すべてのレジスタアドレスにマッチングしなかった場合に、アクセスはスルーされ、そのままバスに流される。S-Mode/U-Modeにおいて、PMPのレジスタエントリが実装されている場合は、レジスタアドレスにマッチングしないアドレスはアクセスはブロックされる。

Lockビットの役割

pmpcfgのLビットは、Lockビットの意味を持っている。このビットを設定するとM-ModeでもProtection判定が適用され、R/W/Xのビット設定もM-Modeでもチェックされるようになる。

Lビットの解除は、RISC-Vのシステムリセットでしか解除することができない。したがってこの設定は半永久的である。