Rocket Chipの動作周波数を上げるべくいろいろ試行していたが、ZynqSmallConfigの場合はどれくらい周波数が上がるのだろう?

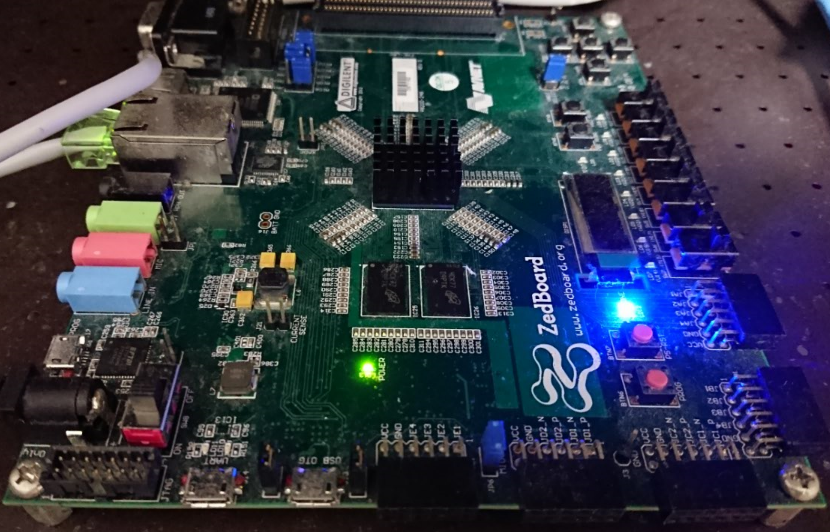

ZedBoardでFPGA向けに合成をする場合にはいくつかオプションがあり、デフォルトではZynqConfig、小さめの構成でZynqSmallConfigというのがある。

ZynqSmallConfigは具体的にどのような構成なのかというと、以下のChiselの資料を見るとなんとなく分かる。

class WithSmallCores extends Config ( topDefinitions = { (pname,site,here) => pname match { case MulDivKey => Some(MulDivConfig()) case FPUKey => None case UseVM => false case NTLBEntries => 4 case BtbKey => BtbParameters(nEntries = 0) case NAcquireTransactors => 2 case _ => throw new CDEMatchError }}, knobValues = { case "L1D_SETS" => 64 case "L1D_WAYS" => 1 case "L1I_SETS" => 64 case "L1I_WAYS" => 1 case "L1D_MSHRS" => 0 case _ => throw new CDEMatchError } )

- MUL/DIV演算器の簡素化 (アンローリングの数などを減らしている)

- FPUを除去

- VMモードを削除

- キャッシュ系のエントリ数を変更

このZynqSmallConfigを使って動作周波数を上げていき、33MHz, 50MHz, 75MHz でFPGAのインプリメントを実行し、タイミングを見てみた。

| WNS[ns] | Slice LUT | Sliced Registers | |

|---|---|---|---|

| 25MHz | 2.010 | 35201 | 15591 |

| 25MHz | 17.706 | 13250 | 7123 |

| 33MHz | 6.182 | 13247 | 7123 |

| 50MHz | 0.728 | 13245 | 7123 |

| 75MHz | -5.299 | 13285 | 7123 |

せいぜいZynqSmallConfigでも50MHzでしか動作しない。というか、Rocket Core の外側のアービタの部分でViolationが出てしまった。

Max Delay Paths

--------------------------------------------------------------------------------------

Slack (VIOLATED) : -5.299ns (required time - arrival time)

Source: top/FPGAZynqTop/adapter/addr_reg[4]/C

(rising edge-triggered cell FDRE clocked by host_clk_i {rise@0.000ns fall@6.667ns period=13.333ns})

Destination: top/FPGAZynqTop/DefaultCoreplex/L2BroadcastHub/iacqTrackerList_0/data_buffer_6_reg[59]/D

(rising edge-triggered cell FDRE clocked by host_clk_i {rise@0.000ns fall@6.667ns period=13.333ns})

Path Group: host_clk_i

Path Type: Setup (Max at Slow Process Corner)

Requirement: 13.333ns (host_clk_i rise@13.333ns - host_clk_i rise@0.000ns)

Data Path Delay: 18.330ns (logic 7.544ns (41.157%) route 10.786ns (58.843%))

Logic Levels: 35 (CARRY4=18 LUT2=1 LUT3=4 LUT4=4 LUT5=2 LUT6=6)

Clock Path Skew: -0.247ns (DCD - SCD + CPR)

Destination Clock Delay (DCD): 5.926ns = ( 19.260 - 13.333 )

Source Clock Delay (SCD): 6.546ns

Clock Pessimism Removal (CPR): 0.373ns

Clock Uncertainty: 0.086ns ((TSJ^2 + DJ^2)^1/2) / 2 + PE

Total System Jitter (TSJ): 0.071ns

Discrete Jitter (DJ): 0.158ns

Phase Error (PE): 0.000ns