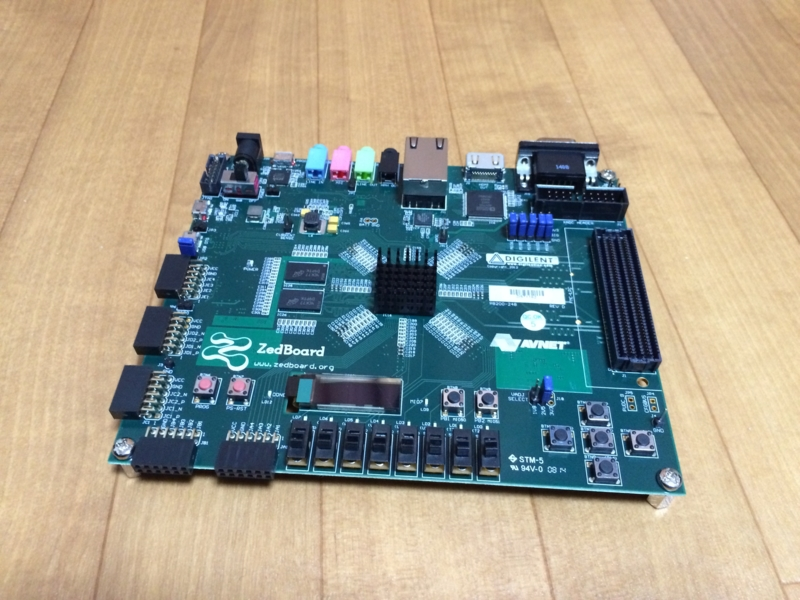

Rocket ChipをFPGAにインプリメントして動作させているが、動作周波数が25MHzに設定されているというのに驚愕した。 ZedBoard自体は100MHzで動くはずだし、HiFive1だって320MHzで動作するような設計だ。 なぜこんなに遅い周波数で設計されているのだろう?

調査してみると、Rocket Chipの動作周波数をコンフィグレーションで変更できることが分かった。 では、Violationが出ない程度に周波数を上げていくとどこまで動作させることができるのだろう?

ZedBoard向けコンフィグレーションにて、Rocket Chipコアの動作周波数を決定しているのはfpga-zynqリポジトリの以下のファイルになる。

- zedboard/src/verilog/clocking.vh

`ifndef _clocking_vh_ `define _clocking_vh_ `define ZYNQ_CLK_PERIOD 10.0 `define RC_CLK_MULT 10.0 `define RC_CLK_DIVIDE 40.0

コメントにも書いてあったが、このパラメータを変えることで、Rocket Chipの動作周波数を変えることが出来る。

従って、現在は で、25MHzに設定されている。では、

RC_CLK_DIVIDEを30.0に設定するとどうなるだろう(つまり33MHzで動かす)?

結論としては、Rocket CoreのFMAパイプラインが盛大にViolationした。こりゃ、25MHzの動作でもギリギリなんだろうな。

Max Delay Paths

--------------------------------------------------------------------------------------

Slack (VIOLATED) : -5.617ns (required time - arrival time)

Source: top/FPGAZynqTop/DefaultCoreplex/tiles_0/fpuOpt/FPUFMAPipe/in_in2_reg[61]/C

(rising edge-triggered cell FDRE clocked by host_clk_i {rise@0.000ns fall@15.000ns period=30.000ns})

Destination: top/FPGAZynqTop/DefaultCoreplex/tiles_0/fpuOpt/FPUFMAPipe/_T_205_data_reg[53]/S

(rising edge-triggered cell FDSE clocked by host_clk_i {rise@0.000ns fall@15.000ns period=30.000ns})

Path Group: host_clk_i

Path Type: Setup (Max at Slow Process Corner)

Requirement: 30.000ns (host_clk_i rise@30.000ns - host_clk_i rise@0.000ns)

Data Path Delay: 34.976ns (logic 17.118ns (48.943%) route 17.858ns (51.057%))

Logic Levels: 55 (CARRY4=29 DSP48E1=3 LUT2=2 LUT3=3 LUT4=2 LUT5=3 LUT6=12 MUXF7=1)

Clock Path Skew: -0.125ns (DCD - SCD + CPR)

Destination Clock Delay (DCD): 6.163ns = ( 36.163 - 30.000 )

Source Clock Delay (SCD): 6.792ns

Clock Pessimism Removal (CPR): 0.505ns

Clock Uncertainty: 0.087ns ((TSJ^2 + DJ^2)^1/2) / 2 + PE

Total System Jitter (TSJ): 0.071ns

Discrete Jitter (DJ): 0.159ns

Phase Error (PE): 0.000ns

ただし、FMAだけならば、浮動小数点を使わないデザインだったらさらに高速化できる気がする。64bitでFPUを除去したデザインとか、Chiselのコンフィグレーションを変えると作れないかしら。