ちまちまRISC-Vの自作プロセッサを改造している。まずは拡張性の向上のためにRISC-Vプロセッサの実装をSystemVerilogに置き換えている。

SystemVerilogの詳細についてはここでは述べないが、いくつか便利な記述があるので紹介。

packed struct

制御信号線周りについて、でコード信号を一度追加すると後でもう一本追加するのが大変だ。そこで、構造体を定義して信号線の拡張を容易にする。

typedef struct packed { logic vld; logic [31: 0] inst; logic [31: 0] pc; logic pr_en; logic pr_taken; } ic_type;

また、logic宣言した回路は、reg,wireの識別を行う必要がなく、組み合わせ回路の時にはalways_comb,順序回路の時はalways_ffで記述できるので便利だ。

- Verilogの場合

wire w_signal; reg r_signal; always @ (posedge clk, negedge reset_n) begin if (!reset_n) begin r_signal <= 1'b0; end else begin r_signal <= ... end end assign w_signal = ...

しかし、SystemVerilogの場合は、logic宣言をしていればalways_comb, always_ffのどちらを利用するかで組み合わせ回路か順序回路化を指定できる。

logic w_signal, r_signal; always_ff @ (posedge clk, negedge reset_n) begin if (!reset_n) begin r_signal <= 1'b0; end else begin r_signal <= ... end end always_comb begin w_signal = ... end

自作CPUの命令発行方式の変更

これらの記述方法を変更して拡張性を上げたのと、命令発行制御方式を変更した。これについては後日詳細を書きたい。

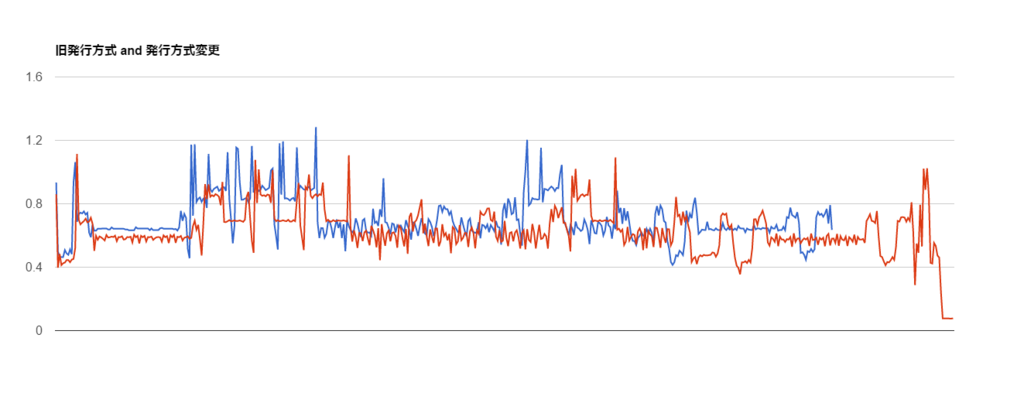

これの影響もあり、Coremarkスコアについては若干下がってしまった。以下はCoremarkのサイクル数だ。

| サイクル数 | stop_time()-start_time() |

|---|---|

| 通常版 | 427167 |

| 発行方式変更版 | 472111 |

全体的にサイクル数が落ちている。これの解析を行う。 青が旧方式で、赤が新方式だ。