前回までで、Vivaod HLSで開発した回路をVivadoにインポートできるIPとして生成した。

次は、Vivadoから開発したIPをインポートして、IPとして利用できるように設定する。

Vivado上で、HLSを使用して開発したIPをインポートする

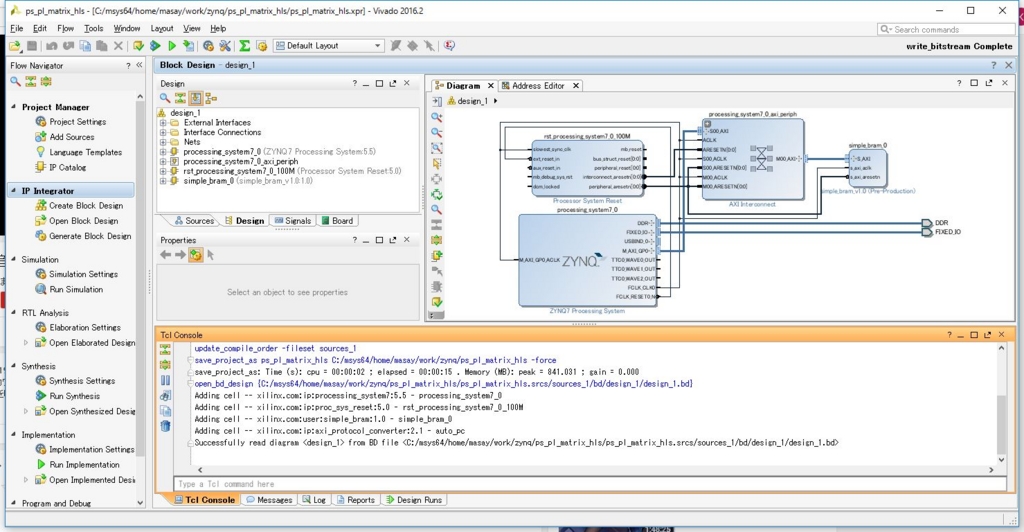

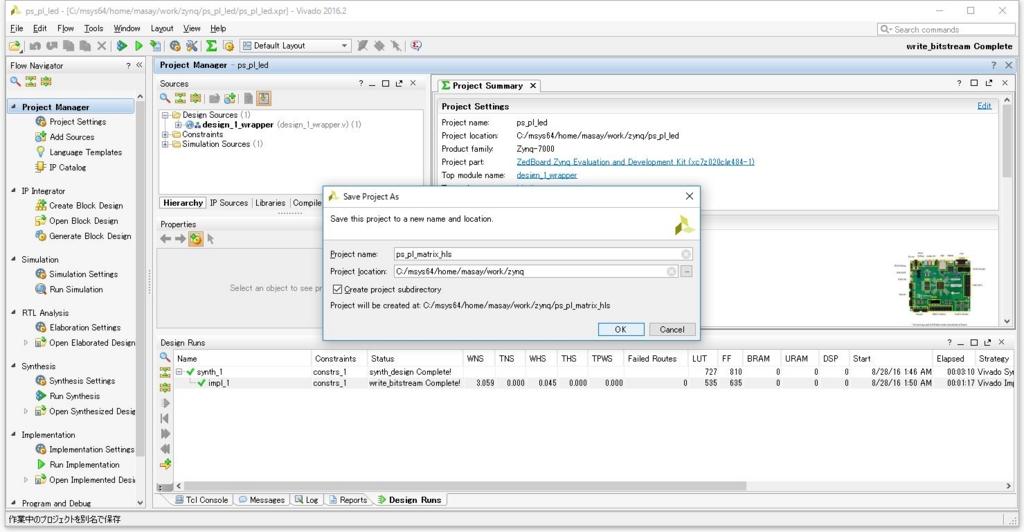

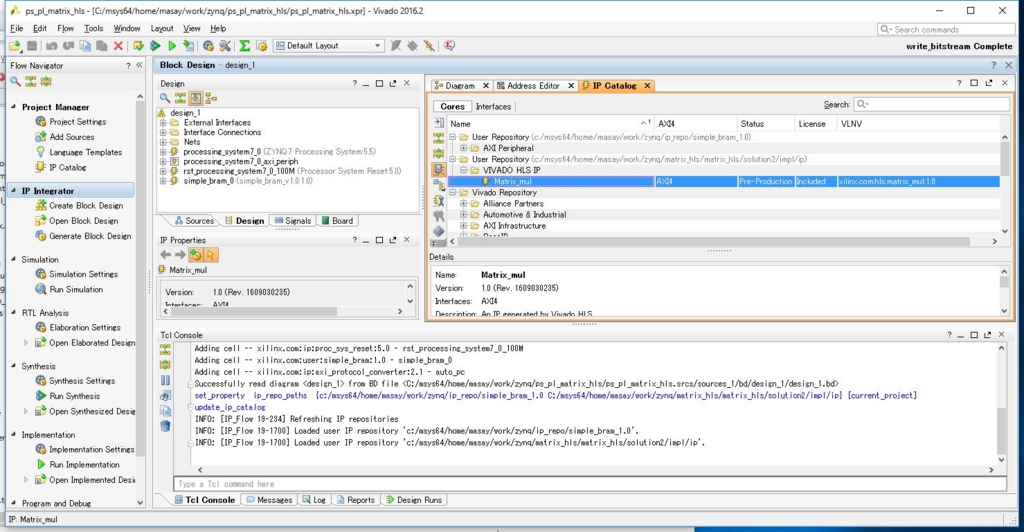

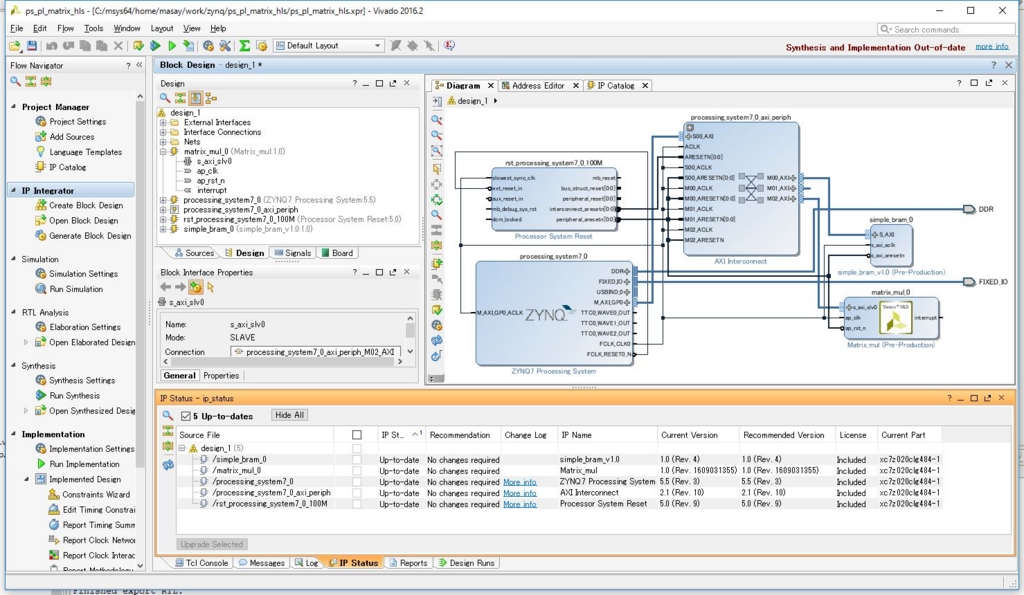

前回、AXIのインタフェースに簡単なBRAMを接続したプロジェクトを利用する。今回は、このプロジェクトをps_pl_matrix_hlsとして新たに保存した。

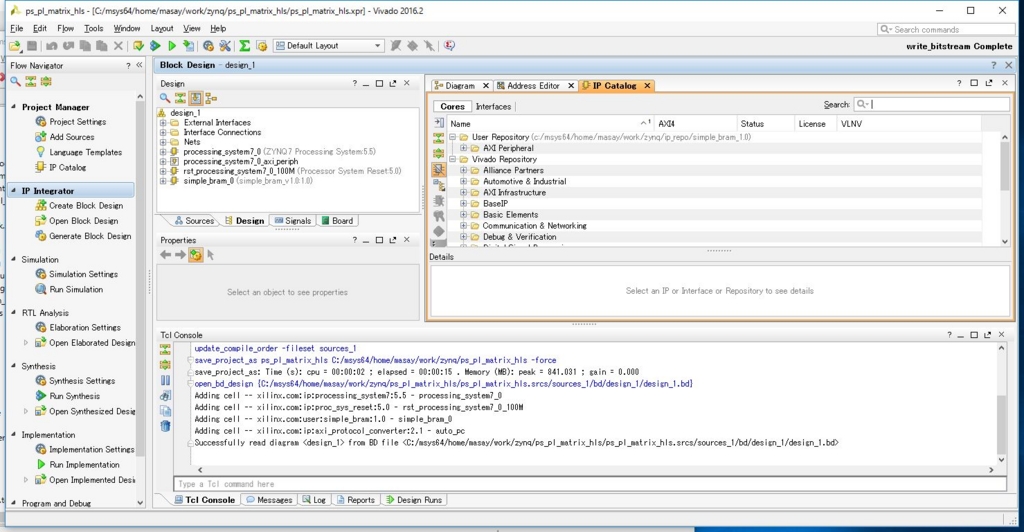

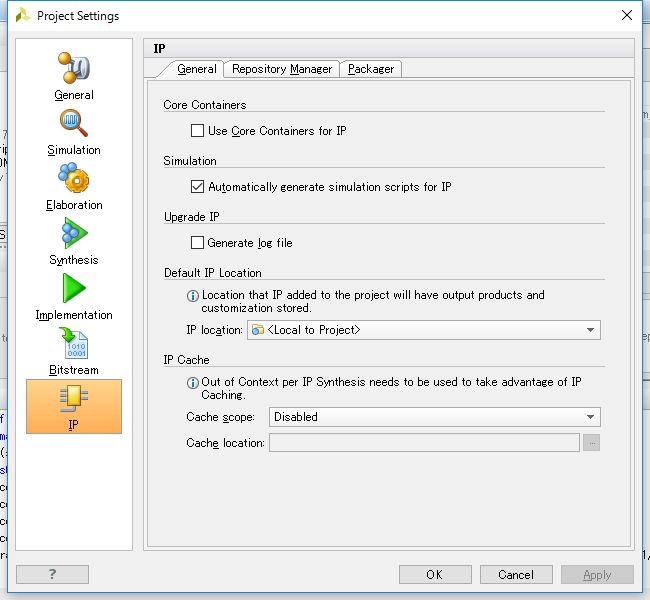

まずはIP CatalogからConfigurationを設定し、[Project Setting]を開く。ここでIPペインを開き、Repository Managerタブを開く。

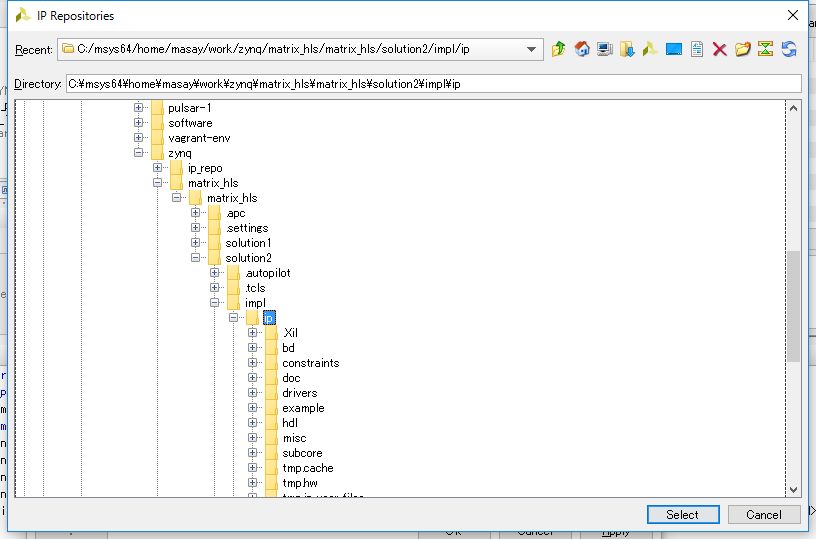

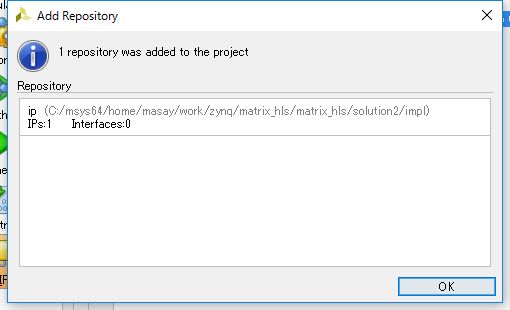

リポジトリマネージャから開発したIPの場所を設定する。

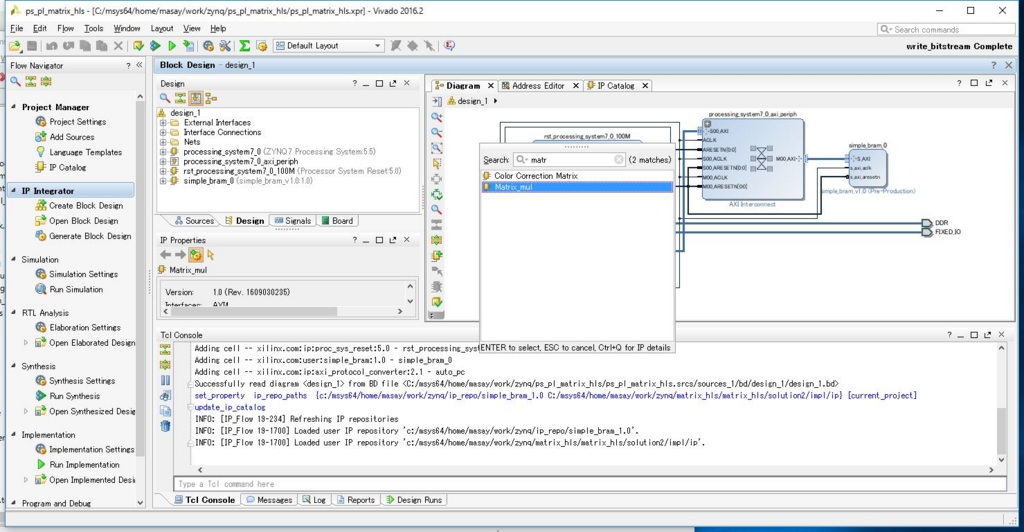

これで、IP Catalogから開発したIPが見えるようになる。

早速、インスタンス化してみよう。さらに、Run Auto Connectionを利用してIPを接続する。

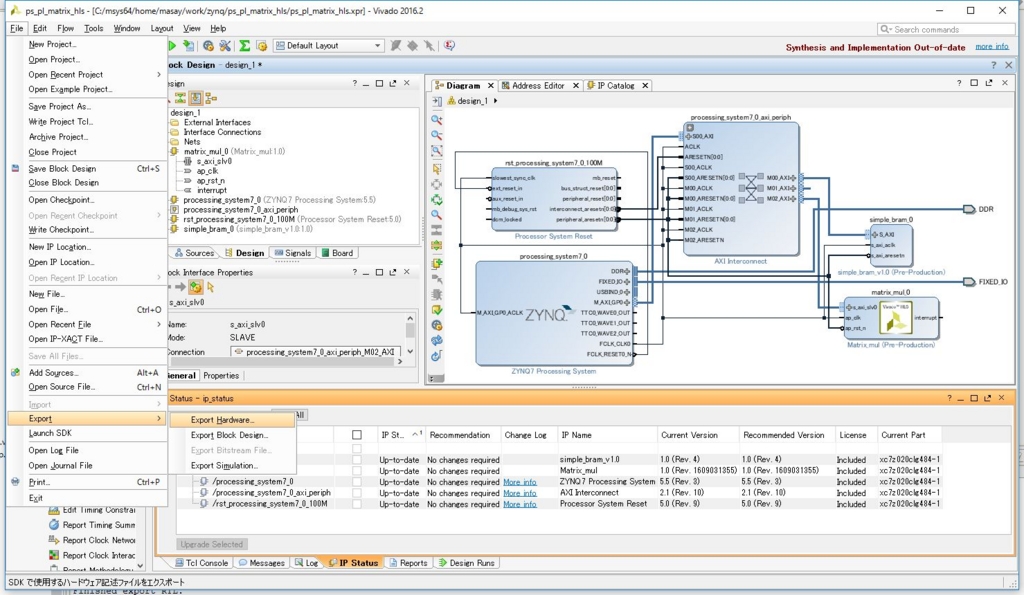

最後にいつもどおり、Generate Bitstreamして、Export Hardware、最後にLaunch SDKを指定してSDKを立ち上げれば完了だ。

ようやくここまで来た。次は制御用のアプリケーションの開発だ。