いわゆるシステムレジスタ群がこのCSR (Control Status Register)に相当する。 CSRはシステムレジスタIDでマッピングされており、これらのアドレスを指定することでアクセスする。

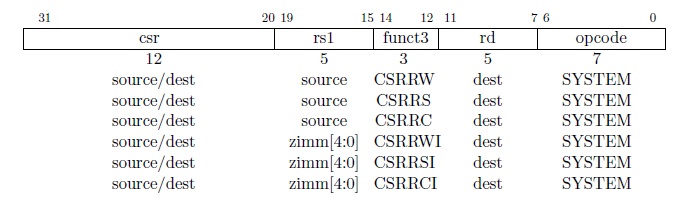

CSRにアクセスできるのは以下の命令になる。

(以下のアーキテクチャ仕様書から抜粋) http://www.eecs.berkeley.edu/Pubs/TechRpts/2015/EECS-2015-49.pdf

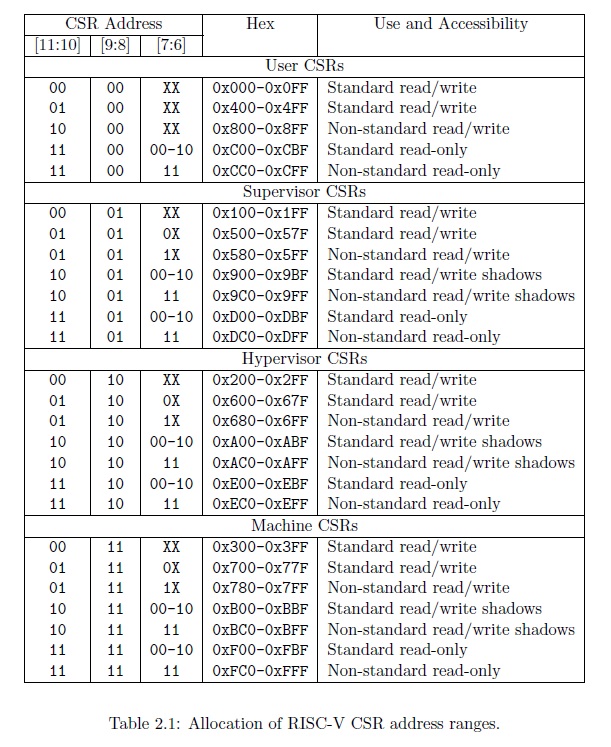

基本的に上記の命令は全てアトミックな命令になっている! どのCSRにアクセスするかは、上位の12ビットのアドレスによって規定されている。後の章になって登場してくるのだが、 このアドレスマップは以下のようになっている。

さらに細かなエンコーディングは後の章で出てくる。

CSRRW (Atomic Read/Write CSR) は、指定されたCSRレジスタの内容と指定した整数レジスタの内容をスワップする。 CSRRWはCSRのレジスタ値を読み取り、整数レジスタのサイズまでゼロ拡張を行って、整数レジスタに値を書き込む。 それと同時に、整数レジスタの値がCSRに書き込まれる。

CSRRS (Atomic Read and Set Bit in CSR) は、CSRの値を読み込み整数レジスタに書き込む。 整数レジスタにCSRの値を読み込み、整数レジスタに格納されているビットポジションのCSRの値を1に更新する。 仕様書の記述があいまいだが、おそらく整数レジスタ側に書き込まれる値は変化せずに、CSR側の値を一方的に更新するのだと思う。 ここらへんは抽象的な表現が多すぎてあまり良く分からない。

CSRRC (Atomic Read and Clear Bit in CSR) は、CSRの値を読み込み整数レジスタに書き込む。CSRRSの逆。 整数レジスタにCSRの値を読み込み、整数レジスタに格納されているビットポジションのCSRの値を0に更新する。

CSRRWI/CSRRSI/CSRRCI はrs1の変わりに、CSRの値をzimm[4:0] で示される即値をゼロ拡張する値を使って更新する。 その再、zimm[4:0]が0の場合は、書き込みを行わないらしい(使いどころが良くわからない。。。5ビットだけ書き込めて何が嬉しいんだ?)