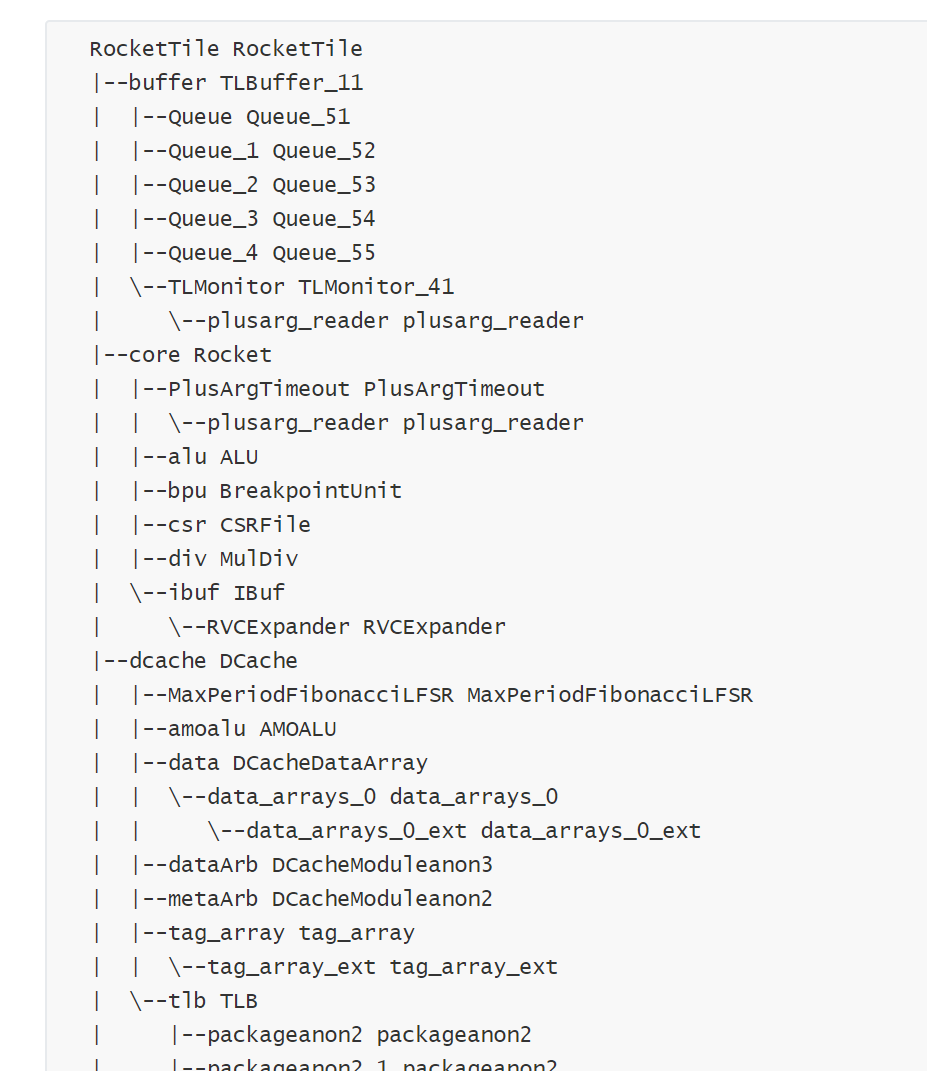

RISC-VのRocket-Chipを勉強していこうと思う。

まずはRocketがどのような階層構成になっているのか、生成されたVerilogを使って把握してみたい。

ずいぶんと古いツールだが、Verilog-Perlの中にvhierというツールが存在する。

久しぶりにVerilog-Perlを使って、Rocket-Chipの階層構造を把握してみることにした。

cd rocket-chip cd emulator make # Verilogを生成 vhier --forest --instance generated-src/*.v ../src/main/resources/vsrc/*.v --top-module RocketTile +define+CLOCK_PERIOD=1.0 -o rocket.hier

生成されたrocket.hierを確認する。

とりあえずこんな感じで生成できた。あとはこれを掘り下げていく。

rocket.hier

RocketTile RocketTile

|--buffer TLBuffer_11

| |--Queue Queue_51

| |--Queue_1 Queue_52

| |--Queue_2 Queue_53

| |--Queue_3 Queue_54

| |--Queue_4 Queue_55

| \--TLMonitor TLMonitor_41

| \--plusarg_reader plusarg_reader

|--core Rocket

| |--PlusArgTimeout PlusArgTimeout

| | \--plusarg_reader plusarg_reader

| |--alu ALU

| |--bpu BreakpointUnit

| |--csr CSRFile

| |--div MulDiv

| \--ibuf IBuf

| \--RVCExpander RVCExpander

|--dcache DCache

| |--MaxPeriodFibonacciLFSR MaxPeriodFibonacciLFSR

| |--amoalu AMOALU

| |--data DCacheDataArray

| | \--data_arrays_0 data_arrays_0

| | \--data_arrays_0_ext data_arrays_0_ext

| |--dataArb DCacheModuleanon3

| |--metaArb DCacheModuleanon2

| |--tag_array tag_array

| | \--tag_array_ext tag_array_ext

| \--tlb TLB

| |--packageanon2 packageanon2

| |--packageanon2_1 packageanon2

| |--packageanon2_10 packageanon2

| |--packageanon2_11 packageanon2

| |--packageanon2_12 packageanon2

| |--packageanon2_13 packageanon2

| |--packageanon2_14 packageanon2

| |--packageanon2_15 packageanon2

...

| |--packageanon2_8 packageanon2

| |--packageanon2_9 packageanon2

| \--pmp PMPChecker

|--dcacheArb HellaCacheArbiter

|--fpuOpt FPU

| |--dfma FPUFMAPipe_1

| | \--fma MulAddRecFNPipe_1

| | |--mulAddRecFNToRaw_postMul MulAddRecFNToRaw_postMul_1

| | |--mulAddRecFNToRaw_preMul MulAddRecFNToRaw_preMul_1

| | \--roundRawFNToRecFN RoundRawFNToRecFN_1

| | \--roundAnyRawFNToRecFN RoundAnyRawFNToRecFN_4

| |--divSqrt DivSqrtRecFN_small

| | |--divSqrtRecFNToRaw DivSqrtRecFNToRaw_small

| | \--roundRawFNToRecFN RoundRawFNToRecFN

| | \--roundAnyRawFNToRecFN RoundAnyRawFNToRecFN

| |--divSqrt_1 DivSqrtRecFN_small_1

| | |--divSqrtRecFNToRaw DivSqrtRecFNToRaw_small_1

| | \--roundRawFNToRecFN RoundRawFNToRecFN_1

| | \--roundAnyRawFNToRecFN RoundAnyRawFNToRecFN_4

| |--fp_decoder FPUDecoder

| |--fpiu FPToInt

| | |--RecFNToIN RecFNToIN

| | |--RecFNToIN_1 RecFNToIN_1

| | \--dcmp CompareRecFN

| |--fpmu FPToFP

| | \--RecFNToRecFN RecFNToRecFN

| | \--RoundAnyRawFNToRecFN RoundAnyRawFNToRecFN_3

| |--ifpu IntToFP

| | |--INToRecFN INToRecFN

| | | \--roundAnyRawFNToRecFN RoundAnyRawFNToRecFN_1

| | \--INToRecFN_1 INToRecFN_1

| | \--roundAnyRawFNToRecFN RoundAnyRawFNToRecFN_2

| \--sfma FPUFMAPipe

| \--fma MulAddRecFNPipe

| |--mulAddRecFNToRaw_postMul MulAddRecFNToRaw_postMul

| |--mulAddRecFNToRaw_preMul MulAddRecFNToRaw_preMul

| \--roundRawFNToRecFN RoundRawFNToRecFN

| \--roundAnyRawFNToRecFN RoundAnyRawFNToRecFN

|--frontend Frontend

| |--btb BTB

| |--fq ShiftQueue

| |--icache ICache

| | |--MaxPeriodFibonacciLFSR MaxPeriodFibonacciLFSR

| | |--data_arrays_0 data_arrays_0_0

| | | \--data_arrays_0_0_ext data_arrays_0_0_ext

| | |--data_arrays_1 data_arrays_0_0

| | | \--data_arrays_0_0_ext data_arrays_0_0_ext

| | \--tag_array tag_array_0

| | \--tag_array_0_ext tag_array_0_ext

| \--tlb TLB_1

| |--packageanon2 packageanon2

| |--packageanon2_1 packageanon2

| |--packageanon2_10 packageanon2

...

| |--packageanon2_9 packageanon2

| \--pmp PMPChecker_1

|--intXbar IntXbar_4

|--intsink IntSyncCrossingSink

| \--SynchronizerShiftReg_w1_d3 SynchronizerShiftReg_w1_d3

|--intsink_1 IntSyncCrossingSink_1

|--intsink_2 IntSyncCrossingSink_2

|--intsink_3 IntSyncCrossingSink_2

|--ptw PTW

| |--arb RRArbiter

| |--packageanon2 packageanon2_78

| \--packageanon2_1 packageanon2_79

\--tlMasterXbar TLXbar_8

|--TLMonitor TLMonitor_39

| \--plusarg_reader plusarg_reader

\--TLMonitor_1 TLMonitor_40

\--plusarg_reader plusarg_reader