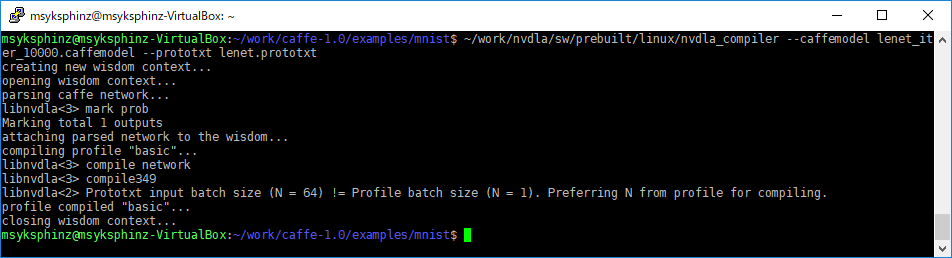

前回はCaffeをインストールして、LeNetを実行した結果をnvdla_compilerに食わせて、NVDLAのバイナリファイルを作成した。

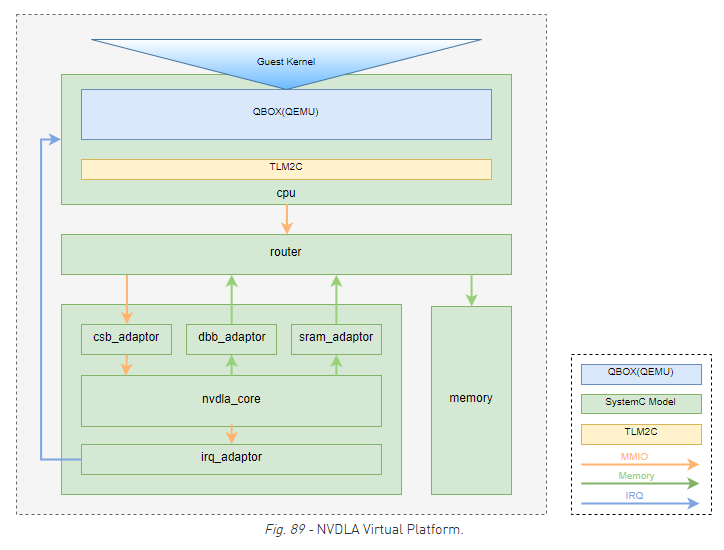

これを実行するためには、NVDLA Virtual Platformを実行してLinuxを立ち上げ、そこでnvdlaを動作させるランタイムプログラムを実行しなければならない。

大まかな手順はNVDLAのウェブサイトに掲載されているが、いろいろとテクニックが必要だ。

NVDLA Virtual Platformの立ち上げ方はこちら。

Caffeのニューラルネットワークのモデルをロードして実行

QEMUにログインすると、まずはホストのディレクトリをマウントしてCaffeのモデルとランタイムプログラムを参照できるようにする。

# QEMUログインして実行 $ mount -t 9p -o trans=virtio r /mnt

QEMUを立ち上げた場所(おそらく高確率でvp)がマウントされるので、そこにファイルを集める。

Caffe で作成したbasic.nvdlaや swリポジトリなどに格納されている画像ファイル(sw/regression/images/*.pgm)などをマウント領域に見えるようにコピーしてくる。

ドライバのロード

まずはドライバをロードする必要がある。sw/prebuilt/linux/をマウントしている場所に移って、以下を実行する。

$ insmod drm.ko $ insmod opendla.ko

nvdla_runtimeを実行する

NVDLAを動かすためのフロントエンドはnvdla_runtimeだ。いろいろオプションを探して、lenetを実行した。

以下ではLeNetのモデルを入力し、入力画像として1の画像(one.pgm)を入力している。

# ./nvdla_runtime --loadable ../lenet/basic.nvdla --image ../lenet/digits/one.pgm creating new runtime context... Emulator starting ppgminfo 1 28 28 pgm2dimg 1 28 28 1 32 896 896 submitting tasks... [ 1429.133975] Enter:dla_read_network_config [ 1429.134275] Exit:dla_read_network_config status=0 [ 1429.134504] Enter: dla_initiate_processors [ 1429.134729] Enter: dla_submit_operation [ 1429.134918] Prepare Convolution operation index 0 ROI 0 dep_count 1 [ 1429.135157] Enter: dla_prepare_operation [ 1429.135409] processor:Convolution group:0, rdma_group:0 available [ 1429.135706] Enter: dla_read_config [ 1429.135976] Exit: dla_read_config [ 1429.136147] Exit: dla_prepare_operation status=0 [ 1429.136336] Enter: dla_program_operation [ 1429.136521] Program Convolution operation index 0 ROI 0 Group[0] ... [ 1651.413376] Enter: dla_free_op_desc op desc index 10 ROI 0 [ 1651.413632] Exit: dla_free_op_desc [ 1651.413793] Exit:dla_op_completion processor SDP group0 status=0 [ 1651.414039] Exit:dla_handle_events, ret:0 [ 1651.414210] Enter:dla_handle_events, processor:PDP [ 1651.414417] Exit:dla_handle_events, ret:0 [ 1651.414603] Enter:dla_handle_events, processor:CDP [ 1651.414791] Exit:dla_handle_events, ret:0 [ 1651.414971] Enter:dla_handle_events, processor:RUBIK [ 1651.415184] Exit:dla_handle_events, ret:0 [ 1651.418539] reset engine done Work Found! Work Done Shutdown signal received, exiting Test pass

一応実行できたぞ。ただしメッセージも出てこないし、正しく推論できたかもわからない。 もう少しプログラムを改造して解析したいのと、NVDLAがどのように動いているのかを見ていきたい。