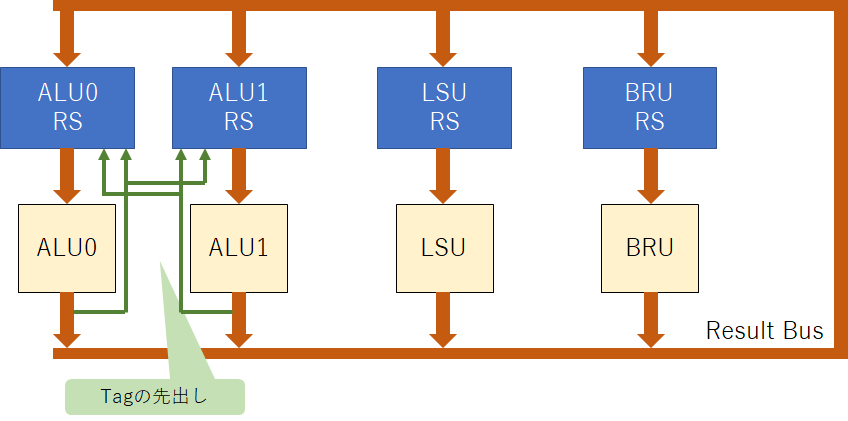

リザベーションステーション(Reservation Station: RS)というのは、アウトオブオーダプロセッサにおける命令待ち合わせ機構の一つで、その命令が必要とするオペランドデータが、リザルトバスに流れてくるの監視している機構である。

リザルトバスに自命令の欲しいオペランドが流れてくるとそれを回収し、命令実行に必要なすべてのオペランドが揃うと命令を発行するという仕組みだ。

Reservation Station - Wikipedia

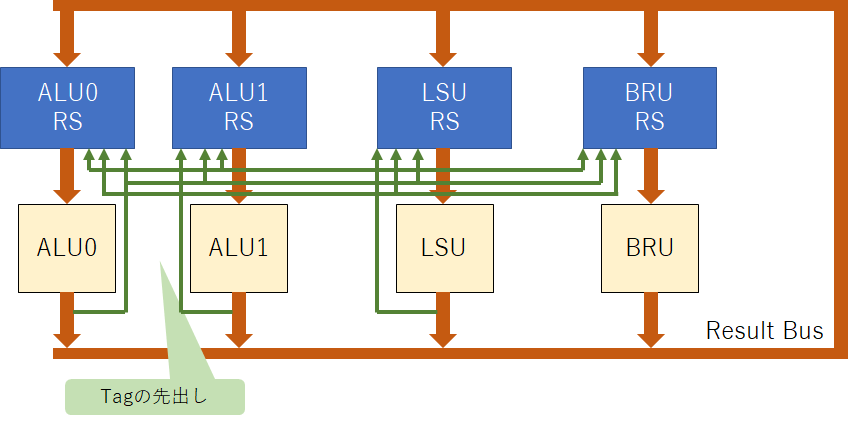

命令を発行するには、RS内でリザルトバスを監視し、すべてのオペランドが揃わないと発行できないが、一般的にこれを高速化する方法の一つとしてタグの先読みという方法がある。

- Understanding the detailed Architecture of AMD’s 64 bit Core

http://www.chip-architect.com/news/2003_09_21_Detailed_Architecture_of_AMDs_64bit_Core.html#1

The Tag busses run one cycle in advance of the result data-busses. The Reservation Station does not need to look at all the busses. The Tag’s sub-index identifies which of the three ALU’s will produce the result. It also knows if the data will come from one of the two cache read ports. It can select the Tag bus in advance rather then having to test all the Tags.

なるほど、オペランドのタグのみ1サイクル早く先出しし、タグが一致した時点で命令を発行、実行ユニット内で実際のリザルトデータを受け取ることで、RSから1サイクル命令を先出しすることができる。

とまあ、この機構は現在のRISC-V自作CPUでも使用している。ただし、ALUx2、LSU、BRUのうち使用しているのはALUx2の互いのリザルトバスだけだ。これを拡張してみるとどうなるのか。

これを、LSUとBRU側にも実装した。LSUからのロードデータの先出をし、タグをLSUからも読めるようにする。 また、BRUに対しても先出のデータを参照できるようにした。

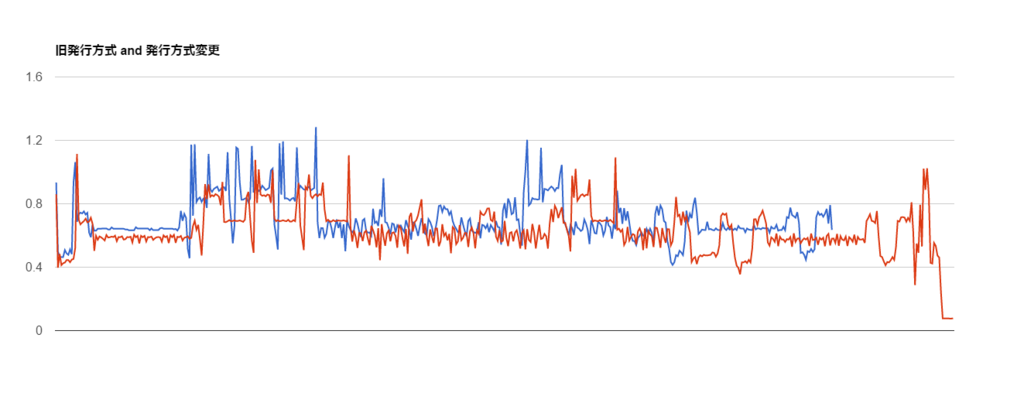

前の実装と比べて、1割程度高速化された。しかしこの時点でCoremarkスコアはまだ3.0を切っている。どうにかして改善せねば。。。