msyksphinz.hatenablog.com

前回、Linuxビルド用のRISC-V GCCの構築が終わったので、次にLinux本体のビルドとシミュレータによる実行をしてみたい。

github.com

まずはRISC-V用Linuxの作業リポジトリと、Linux本体を取得してくる。

curl -L https://cdn.kernel.org/pub/linux/kernel/v4.x/linux-4.6.2.tar.xz | tar -xJ

cd linux-4.6.2

git init

git remote add -t master origin https://github.com/riscv/riscv-linux.git

git fetch

git checkout -f -t origin/master

git remote set-branches --add origin linux-4.6.y-riscv

git fetch

make ARCH=riscv defconfig

make -j4 ARCH=riscv vmlinux

これでLinuxの本体であるvmlinuxが生成される。生成される場所を今回は /home/msyksphinz/work/linux-4.6.2/vmlinuxとしている。

github.com

BusyBox - Wikipedia

BusyBoxというのは、Linuxの一連のコマンド群をまとめたものだ。

私もあまり詳細は知らないのだが、MS-DOSのcmd.exeみたいなものだろうか。

特定用途のLinuxディストリビューションや組み込みシステムに適しており、「組み込みLinuxの十徳ナイフ」とも呼ばれている。

cd ~/work/riscv-tools/

curl -L http://busybox.net/downloads/busybox-1.21.1.tar.bz2 | tar -xj

cd busybox-1.21.1

make allnoconfig

make -j

これにより、busyboxが生成される。

ls -l

...

drwxr-xr-x 5 msyksphinz msyksphinz 4096 3月 25 14:33 shell

drwxr-xr-x 3 msyksphinz msyksphinz 4096 3月 25 14:33 util-linux

drwxr-xr-x 2 msyksphinz msyksphinz 4096 3月 25 14:33 sysklogd

drwxr-xr-x 2 msyksphinz msyksphinz 16384 3月 25 14:33 libbb

-rw-rw-r-- 1 msyksphinz msyksphinz 15998 3月 25 14:33 busybox_unstripped.out

-rw-rw-r-- 1 msyksphinz msyksphinz 37906 3月 25 14:33 busybox_unstripped.map

-rwxrwxr-x 1 msyksphinz msyksphinz 13840 3月 25 14:33 busybox_unstripped

-rwxrwxr-x 1 msyksphinz msyksphinz 10344 3月 25 14:33 busybox

Linuxのルートファイルシステムを構築するために、イメージファイルの作成を行う。

cd ~/work/riscv-tools/root_bin/

dd if=/dev/zero of=root.bin bs=1M count=64

mkfs.ext2 -F root.bin

mkdir mnt

sudo mount -o loop root.bin mnt

cd mnt

sudo mkdir -p bin etc dev lib proc sbin sys tmp usr usr/bin usr/lib usr/sbin

sudo cp ~/work/riscv-tools/busybox-1.21.1/busybox bin

curl -L https://www.ocf.berkeley.edu/~qmn/linux/linux-inittab > etc/inittab

linux-inittabはgithubの説明の場所には存在していなかったので、別の場所から取ってきた。

busyboxをリンクする。

cd sbin

ln -s ../bin/busybox init

cd ../../

sudo umount mnt

bblの再構築

Spikeで完成したLinuxをシミュレーションする前に、bblの再構築を行わなければならない。vmlinuxの場所を指定してriscv-pkを再構築する。

cd ~/work/riscv-tools/

export RISCV=/home/msyksphinz/riscv

. build.common

CC= CXX= build_project riscv-pk --prefix=$RISCV --host=riscv64-unknown-elf --with-payload=/home/msyksphinz/work/linux-4.6.2/vmlinux

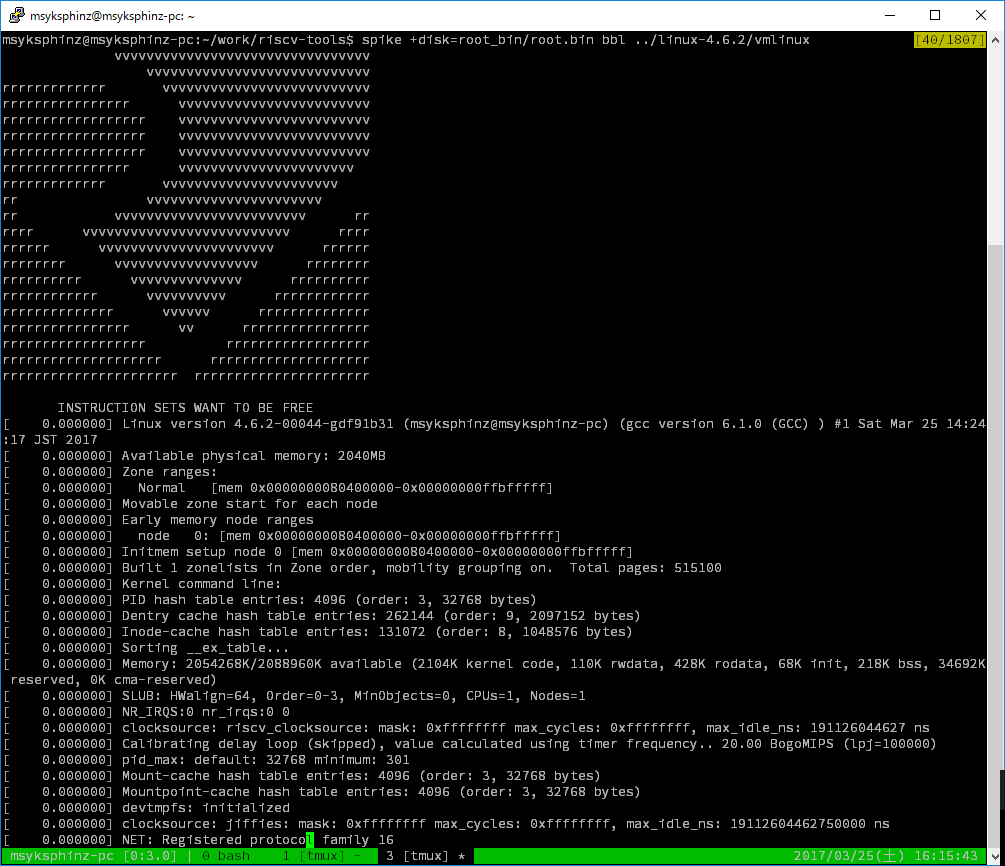

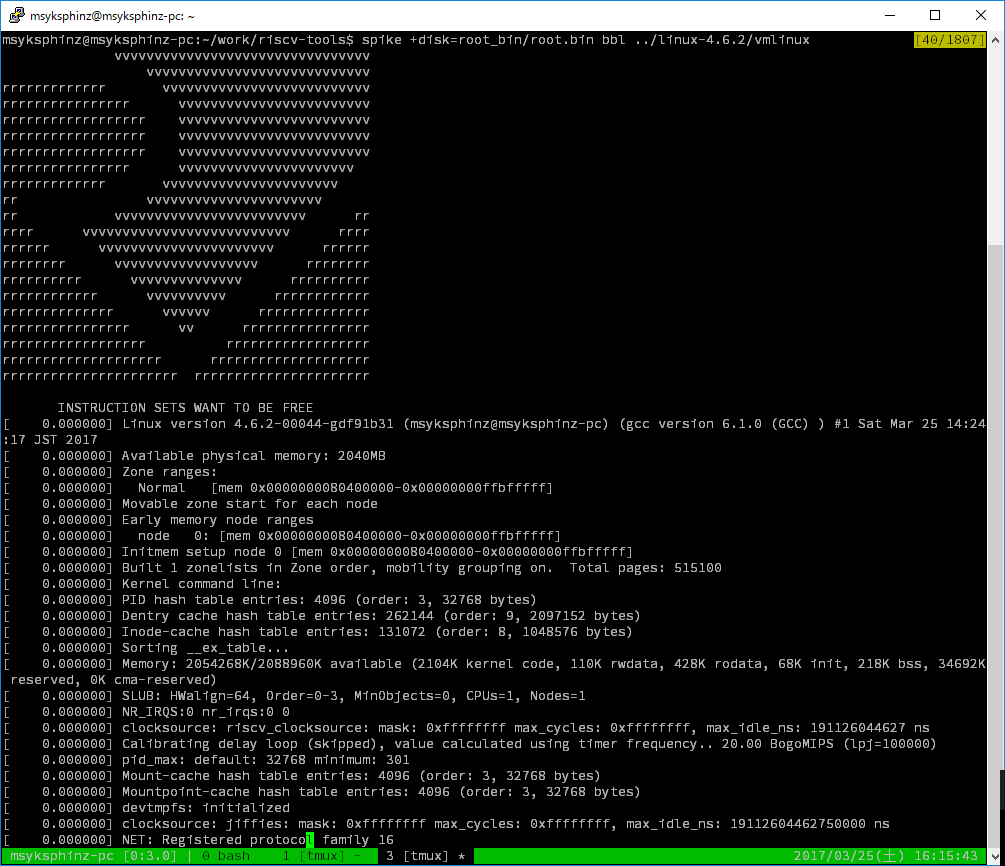

Spikeでのシミュレーション

これでSpikeを走らせてみたのだが、どうも起動途中に失敗してしまった。

spike +disk=root_bin/root.bin bbl ../linux-4.6.2/vmlinux

...

[ 0.040000] Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(0,0)

[ 0.040000] CPU: 0 PID: 1 Comm: swapper Not tainted 4.6.2-00044-gdf91b31 #1

[ 0.040000] Call Trace:

[ 0.040000] [<ffffffff80012fc8>] walk_stackframe+0x0/0xc8

[ 0.040000] [<ffffffff80056e90>] panic+0xec/0x20c

[ 0.040000] [<ffffffff800011d8>] mount_block_root+0x248/0x328

[ 0.040000] [<ffffffff8000292c>] ksysfs_init+0x10/0x40

[ 0.040000] [<ffffffff80001488>] prepare_namespace+0x148/0x198

[ 0.040000] [<ffffffff80000da0>] kernel_init_freeable+0x1c8/0x200

[ 0.040000] [<ffffffff8021b160>] rest_init+0x80/0x84

[ 0.040000] [<ffffffff8021b174>] kernel_init+0x10/0x11c

[ 0.040000] [<ffffffff8021b160>] rest_init+0x80/0x84

[ 0.040000] [<ffffffff80011c0c>] ret_from_syscall+0x10/0x14

[ 0.040000] ---[ end Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(0,0)

: msyksphinz@msyksphinz-pc:~/work/riscv-tools$ ^C

解析の必要あり。