個人の開発を記録するためにRedmineを導入したが、githubとの連携をまだ実現していなかった。

githubとの連携を実現するための情報はたくさんあるが、bitnamiで構築したRedmineとgithubはどのように連携すればよいのだろうか?調査してみた。

実現したいこととしては、githubに対してpushすると、自動的にRedmineのリポジトリもアップデートして欲しい。

GithubとRedmineを連携させる仕組み

ここでは、redmine_github_hookというプラグインを使用した。その名のとおりRedmineとGithubを連携させるためのプラグインだ。

CentOS 6.8にインストールした場合は、Rubyのバージョンなどを上げないとうまく行かないようだったが、基本的にマニュアルどおりにインストールすることが出来る。

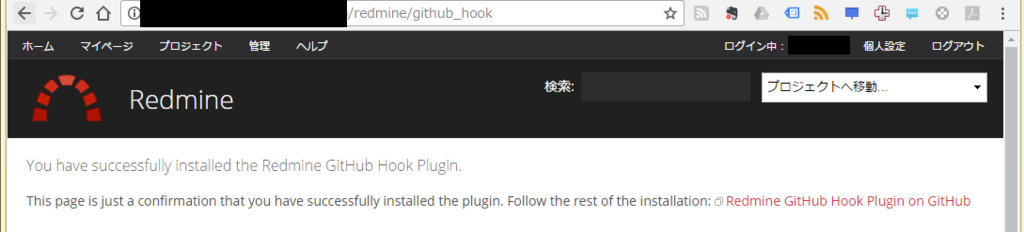

インストールが完了すると、Redmineを立ち上げて、http://redmineのページ/github_hookにアクセスしてきちんとメッセージが出るかを確認する。

redmine_github_hookの仕組みはこうだ。まずgithubに対してpushが実行されると、webhookを通じて対象Redmineのgithub_hookに通知が発行される。 すると、Redmineの存在するサーバにgitリポジトリのクローンが作られており、それをアップデートさせる、という仕組みだ。

(https://github.com/koppen/redmine_github_hook より画像抜粋)

これらの操作は、詰まるところがRedmineが実施している。

多くのredmine_github_hooksの解説記事では、Redmineサーバ上に配置するgitリポジトリのクローンを、マシン内でgitを引くための専用アカウントや、redmineを実行しているアカウントであるapacheを設定している。

しかし、Bitnamiで設定したRedmineの場合はどうだろうか?

ps aux | grep httpd daemon 1976 0.0 0.3 394960 1756 ? S 02:48 0:00 /opt/redmine-3.3.1-0/apache2/bin/httpd.bin -f /opt/redmine-3.3.1-0/apache2/conf/httpd.conf

daemonというユーザが実行している。さらにdaemonについて調べると、

less /etc/passwd ... daemon:x:2:2:daemon:/sbin:/sbin/nologin ...

ホームディレクトリが/sbinか、、、なかなか難しいな。/sbin/だとsshキーを作ったとしても/sbin/.ssh/を置くのはちょっと厳しいかもしれない。別の場所を作っておこう。ここでは/home/daemon/とした。

less /etc/passwd ... daemon:x:2:2:daemon:/home/daemon:/sbin/nologin ...

/home/daemon/.sshにgithubとの連携を行うためのsshキーを作成し、githubと連携させた。このためには、いったんdaemonユーザに切り替わる必要がある。

sudo -s -u daemon (daemonユーザにて) ssh-keygen -t rsa

Redmine用サーバにgitリポジトリのミラーをcloneする

Redmineサーバにgitリポジトリのミラーをcloneし、Redmineと同期させる。ここでは、まずいったんdaemonユーザにsuし、リポジトリをクローンした。

sudo -s -u daemon cd /opt/repos git clone --mirror git@github.com:msyksphinz/swimmer_iss.git

bash-4.1$ pwd /opt/repos bash-4.1$ ls -ltr total 4 drwxr-xr-x 7 daemon daemon 4096 Feb 12 01:20 swimmer_iss.git

GithubのWebhookに、リポジトリのpushを通知させる

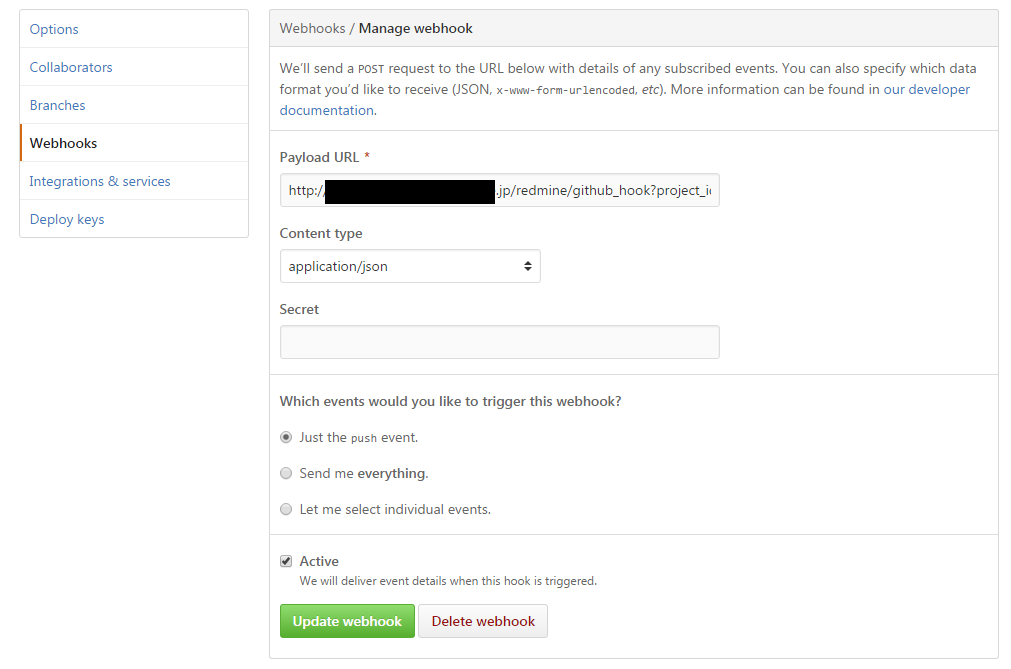

最後に、gitリポジトリにpushがなされた場合、対象のRedmineに通知が発行されるようにしたい。 これにより、Redmineサーバ側のリポジトリがfetchされ、情報がアップデートされる仕組みだ。

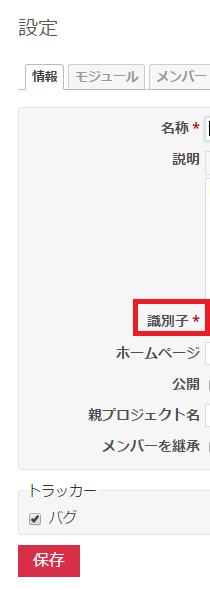

githubのリポジトリ設定欄から「Webhook」の項目を設定する。http://redmineサーバ名/redmine/github_hook?project_id=xxxというフォーマットで指定する。xxxの部分は、Redmineのプロジェクトの識別子を記入する。

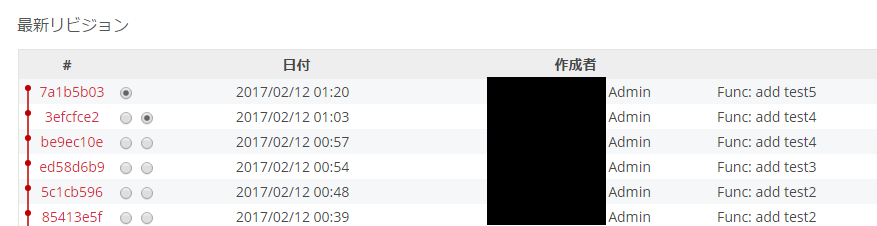

これでRedmineとのリポジトリ連携が完了した。ためしに、githubに向けてpushを通知してみよう。

echo test >> test && git commit -a -m "Func: add test5" && git push origin temp

雑なコミットだな!Redmine側には何か通知が行っているだろうか?Redmineのproduction.logを確認しよう。

Started POST "/redmine/github_hook?project_id=magnetor-1" for 192.30.252.34 at 2017-02-12 01:20:46 +0900

Processing by GithubHookController#index as */*

Parameters: {"ref"=>"refs/heads/temp", "before"...

...

Current user: anonymous

GithubHook: Redmine repository updated: swimmer_iss (Git: 5311.4ms, Redmine: 456.5ms)

Completed 200 OK in 5794ms (Views: 2.0ms | ActiveRecord: 71.8ms)

GithubHookが働いて、リポジトリのアップデートがうまく行ったようだ。